Temporizator digital 14h

Digital Timer 14h

Digital Timer 14h

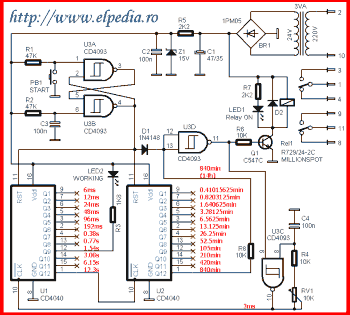

Temporizatorul digital prezentat, bazat pe circuite logice CMOS, actioneaza un releu electromagnetic in momentul apasarii scurte a unui pushbuton, releul ramanand cuplat pe o durata de aproximativ 14 ore. La expirarea intervalului de timp mentionat, releul decupleaza, deconectand dispozitivul comandat, un nou ciclu se poate initia printr-o noua apasare pe buton.

Functionare temporizator la revenire 14h

In momentul alimentarii timerul se reseteaza automat prin grupul R2,C3 („power-on reset”). Condensatorul C3 se incarca de la tensiunea de 15V existenta pe dioda zener Z1. La aplicarea tensiunii de alimentare, condensatorul C3 initial descarcat, isi trage curentul de incarcare comportandu-se in primul moment ca un scurtcircuit, curentul fiind limitat de R2, pinul 6 al lui U3B este tras la masa, iesirea de la pinul 4/U3 a bistabilului R-S implementat cu portile U3A-U3B trece in UNU logic, acest nivel se aplica pe linia de reset a celor 2 numaratoare, U1 si U2 (pini 12), asigurand resetarea, adica nivel ZERO logic pe toate iesirile Q1-Q12 ale numaratoarelor U1,U2.

Baza de timp este construita cu un oscilator CMOS Schmit de tip CD4093, folosindu-se o poarta din cele 4 existente in capsula,si anume U3C. Oscilatorul este comandabil, el functioneaza atata timp cat pe pinul 9 al portii este prezent nivel logic UNU, fiind blocat cand nivelul logic pe acest pin este ZERO. Perioada a semnalului semnalului generat este de 3 milisecunde, durata temporizarii fiind de 14 ore (840 minute), durata necesara numararii acestora de catre cele doua numaratoare U1, U2, cascadate asincron, care totalizeaza impreuna 24 biti.

Temporizarea este initiata de apasarea butonului PB1 (START), care declanseaza bistabilul asincron RS alcatuit cu portile U3A, U3B. Am aratat mai sus modul cum in momentul alimentarii, iesirea portii U3B de la pinul 4, devine 1 LOGIC. Iesirea complementara a bistabilului, adica pinul 3 al portii U3A va fi, evident, in ZERO logic, nivel care este aplicat si pe pinul 5 al portii U3B. Cum poarta U3B prezinta nivele logice diferite pe cele doua intrari ale sale, iesirea va sta in UNU logic, conform tabelei de adevar a circuitului SI-NU (NAND), tinand in UNU logic linia de RESET la care sunt legati pinii 11 ai numaratoarelor U1, U2. Ca atare, numaratoarele vor fi blocate, prezentand nivel logic ZERO pe toate iesirile. In momentul cand se apasa pe butonul PB1, se pune la masa pinul 1 al portii U3A. Cum una din intrarile acestei porti prezinta nivel ZERO logic, iesirea corespunzatoare de la pinul 3 va bascula in UNU logic, conform aceleiasi tabele de adevar. Acest nivel e aplicat si pe intrarea de la pinul 5 a portii U3B, iar cum aceasta prezinta deja UNU logic pe cealalta intrare (pin 6), iesirea sa de la pin 4, adica linia de RESET trece in ZERO logic, deblocand numaratoarele, care vor demara procesul de numarare a impulsurilor primite pe pinul de ceas.

Semnalul de tact generat de operatorul NAND Schmit U3C, este aplicat intrarii de ceas, de la pin 10 a numaratorului U1, folosit ca numarator de 12 biti, semnalul de iesire a acestuia fiind cel cules de la iesirea Q12 (pin 1). De la acest numarator se mai foloseste si iesirea Q9, care comanda un LED (LED2) folosit ca martor care indica faptul ca procesul de temporizare este in curs, clipind intermitent cu perioada de cca 1.5 secunde pe toata durata temporizarii.

Numaratorul U1 este cascadat asincron cu numaratorul U2, de acelasi tip – CD4040, de la care este utilizata iesirile Q12, care-si schimba starea la expirarea duratei de temporizare, moment cand trece in UNU logic. Acest nivel, aplicat intrarilor operatorului U3D, la pinii 12 si 13, va produce trecerea iesirii de la pinul 11 a portii in ZERO logic, ducand la blocare tranzistorului Q1, ca urmare bobina releului REL1 nu mai primeste tensiune, acesta fiind dezactivat, LED1 se stinge.

Nivelul ZERO logic de la iesirea portii U3D (pin11) se plica si pe una din intrarile portii U3C, mai exact pe pinul 9 a acesteia, astfel ca, din acest moment, iesirea acesteia (pin 10) este fortata in UNU logic indiferent de starea celeilalte intrari (pin 8), blocand oscilatorul astfel ca procesul de temporizare incheiat.

Initierea unui nou proces de temporizare este posibila prin reapasarea butonului PB1 (START), ceea ce va declansa mecanismul descris anterior. Nivelul logic UNU care apare la pin 11/U3D si deschide tranzistorul Q1 ce declanseaza releul, e aplicat si pe intrarea de la pin 9 a U3C, activand oscilatorul ce va genera impulsurile care se aplica numaratorului, intrarea de la pin 9 putand fi considerata intrare de ENABLE, activata cu UNU logic. Este usor de observat, privind tabela de adevar a portii NAND, ca un zero logic prezent pe oricare din intrari forteaza iesirea acesteia in zero logic, iar existenta unui unu logic pe una din intrari, face posibila existenta pe iesire a oricareia din cele 2 stari posibile (0, 1), in functie de nivelul aplicat pe cealalta intrare.

Baza de timp este construita cu un oscilator CMOS Schmit de tip CD4093, folosindu-se o poarta din cele 4 existente in capsula,si anume U3C. Oscilatorul este comandabil, el functioneaza atata timp cat pe pinul 9 al portii este prezent nivel logic UNU, fiind blocat cand nivelul logic pe acest pin este ZERO. Perioada a semnalului semnalului generat este de 3 milisecunde, durata temporizarii fiind de 14 ore (840 minute), durata necesara numararii acestora de catre cele doua numaratoare U1, U2, cascadate asincron, care totalizeaza impreuna 24 biti.

Temporizarea este initiata de apasarea butonului PB1 (START), care declanseaza bistabilul asincron RS alcatuit cu portile U3A, U3B. Am aratat mai sus modul cum in momentul alimentarii, iesirea portii U3B de la pinul 4, devine 1 LOGIC. Iesirea complementara a bistabilului, adica pinul 3 al portii U3A va fi, evident, in ZERO logic, nivel care este aplicat si pe pinul 5 al portii U3B. Cum poarta U3B prezinta nivele logice diferite pe cele doua intrari ale sale, iesirea va sta in UNU logic, conform tabelei de adevar a circuitului SI-NU (NAND), tinand in UNU logic linia de RESET la care sunt legati pinii 11 ai numaratoarelor U1, U2. Ca atare, numaratoarele vor fi blocate, prezentand nivel logic ZERO pe toate iesirile. In momentul cand se apasa pe butonul PB1, se pune la masa pinul 1 al portii U3A. Cum una din intrarile acestei porti prezinta nivel ZERO logic, iesirea corespunzatoare de la pinul 3 va bascula in UNU logic, conform aceleiasi tabele de adevar. Acest nivel e aplicat si pe intrarea de la pinul 5 a portii U3B, iar cum aceasta prezinta deja UNU logic pe cealalta intrare (pin 6), iesirea sa de la pin 4, adica linia de RESET trece in ZERO logic, deblocand numaratoarele, care vor demara procesul de numarare a impulsurilor primite pe pinul de ceas.

Semnalul de tact generat de operatorul NAND Schmit U3C, este aplicat intrarii de ceas, de la pin 10 a numaratorului U1, folosit ca numarator de 12 biti, semnalul de iesire a acestuia fiind cel cules de la iesirea Q12 (pin 1). De la acest numarator se mai foloseste si iesirea Q9, care comanda un LED (LED2) folosit ca martor care indica faptul ca procesul de temporizare este in curs, clipind intermitent cu perioada de cca 1.5 secunde pe toata durata temporizarii.

Numaratorul U1 este cascadat asincron cu numaratorul U2, de acelasi tip – CD4040, de la care este utilizata iesirile Q12, care-si schimba starea la expirarea duratei de temporizare, moment cand trece in UNU logic. Acest nivel, aplicat intrarilor operatorului U3D, la pinii 12 si 13, va produce trecerea iesirii de la pinul 11 a portii in ZERO logic, ducand la blocare tranzistorului Q1, ca urmare bobina releului REL1 nu mai primeste tensiune, acesta fiind dezactivat, LED1 se stinge.

Nivelul ZERO logic de la iesirea portii U3D (pin11) se plica si pe una din intrarile portii U3C, mai exact pe pinul 9 a acesteia, astfel ca, din acest moment, iesirea acesteia (pin 10) este fortata in UNU logic indiferent de starea celeilalte intrari (pin 8), blocand oscilatorul astfel ca procesul de temporizare incheiat.

Initierea unui nou proces de temporizare este posibila prin reapasarea butonului PB1 (START), ceea ce va declansa mecanismul descris anterior. Nivelul logic UNU care apare la pin 11/U3D si deschide tranzistorul Q1 ce declanseaza releul, e aplicat si pe intrarea de la pin 9 a U3C, activand oscilatorul ce va genera impulsurile care se aplica numaratorului, intrarea de la pin 9 putand fi considerata intrare de ENABLE, activata cu UNU logic. Este usor de observat, privind tabela de adevar a portii NAND, ca un zero logic prezent pe oricare din intrari forteaza iesirea acesteia in zero logic, iar existenta unui unu logic pe una din intrari, face posibila existenta pe iesire a oricareia din cele 2 stari posibile (0, 1), in functie de nivelul aplicat pe cealalta intrare.

Aplicatii

Un astfel de timer poate fi util in multe aplicatii, printre care amintim controlul duratei de incarcare a unor acumulatoare NiCd sau NiMH.